ਐਪੀਟੈਕਸੀਅਲ ਪਰਤ ਇੱਕ ਖਾਸ ਸਿੰਗਲ ਕ੍ਰਿਸਟਲ ਫਿਲਮ ਹੈ ਜੋ ਐਪੀਟੈਕਸੀਅਲ ਪ੍ਰਕਿਰਿਆ ਦੁਆਰਾ ਵੇਫਰ 'ਤੇ ਉਗਾਈ ਜਾਂਦੀ ਹੈ, ਅਤੇ ਸਬਸਟਰੇਟ ਵੇਫਰ ਅਤੇ ਐਪੀਟੈਕਸੀਅਲ ਫਿਲਮ ਨੂੰ ਐਪੀਟੈਕਸੀਅਲ ਵੇਫਰ ਕਿਹਾ ਜਾਂਦਾ ਹੈ। ਕੰਡਕਟਿਵ ਸਿਲੀਕਾਨ ਕਾਰਬਾਈਡ ਸਬਸਟਰੇਟ 'ਤੇ ਸਿਲੀਕਾਨ ਕਾਰਬਾਈਡ ਐਪੀਟੈਕਸੀਅਲ ਪਰਤ ਨੂੰ ਵਧਾ ਕੇ, ਸਿਲੀਕਾਨ ਕਾਰਬਾਈਡ ਸਮਰੂਪ ਐਪੀਟੈਕਸੀਅਲ ਵੇਫਰ ਨੂੰ ਅੱਗੇ ਸ਼ੌਟਕੀ ਡਾਇਡਸ, MOSFETs, IGBTs ਅਤੇ ਹੋਰ ਪਾਵਰ ਡਿਵਾਈਸਾਂ ਵਿੱਚ ਤਿਆਰ ਕੀਤਾ ਜਾ ਸਕਦਾ ਹੈ, ਜਿਨ੍ਹਾਂ ਵਿੱਚੋਂ 4H-SiC ਸਬਸਟਰੇਟ ਸਭ ਤੋਂ ਵੱਧ ਵਰਤਿਆ ਜਾਂਦਾ ਹੈ।

ਸਿਲੀਕਾਨ ਕਾਰਬਾਈਡ ਪਾਵਰ ਡਿਵਾਈਸ ਅਤੇ ਪਰੰਪਰਾਗਤ ਸਿਲੀਕਾਨ ਪਾਵਰ ਡਿਵਾਈਸ ਦੀ ਵੱਖ-ਵੱਖ ਨਿਰਮਾਣ ਪ੍ਰਕਿਰਿਆ ਦੇ ਕਾਰਨ, ਇਸ ਨੂੰ ਸਿਲੀਕਾਨ ਕਾਰਬਾਈਡ ਸਿੰਗਲ ਕ੍ਰਿਸਟਲ ਸਮੱਗਰੀ 'ਤੇ ਸਿੱਧਾ ਨਹੀਂ ਬਣਾਇਆ ਜਾ ਸਕਦਾ ਹੈ। ਵਾਧੂ ਉੱਚ-ਗੁਣਵੱਤਾ ਵਾਲੀ ਐਪੀਟੈਕਸੀਅਲ ਸਮੱਗਰੀ ਨੂੰ ਕੰਡਕਟਿਵ ਸਿੰਗਲ ਕ੍ਰਿਸਟਲ ਸਬਸਟਰੇਟ 'ਤੇ ਉਗਾਇਆ ਜਾਣਾ ਚਾਹੀਦਾ ਹੈ, ਅਤੇ ਵੱਖ-ਵੱਖ ਉਪਕਰਣਾਂ ਨੂੰ ਐਪੀਟੈਕਸੀਲ ਪਰਤ 'ਤੇ ਤਿਆਰ ਕੀਤਾ ਜਾਣਾ ਚਾਹੀਦਾ ਹੈ। ਇਸ ਲਈ, ਐਪੀਟੈਕਸੀਅਲ ਪਰਤ ਦੀ ਗੁਣਵੱਤਾ ਦਾ ਡਿਵਾਈਸ ਦੀ ਕਾਰਗੁਜ਼ਾਰੀ 'ਤੇ ਬਹੁਤ ਪ੍ਰਭਾਵ ਹੁੰਦਾ ਹੈ. ਵੱਖ-ਵੱਖ ਪਾਵਰ ਯੰਤਰਾਂ ਦੀ ਕਾਰਗੁਜ਼ਾਰੀ ਵਿੱਚ ਸੁਧਾਰ ਐਪੀਟੈਕਸੀਅਲ ਪਰਤ ਦੀ ਮੋਟਾਈ, ਡੋਪਿੰਗ ਇਕਾਗਰਤਾ ਅਤੇ ਨੁਕਸ ਲਈ ਉੱਚ ਲੋੜਾਂ ਨੂੰ ਵੀ ਅੱਗੇ ਰੱਖਦਾ ਹੈ।

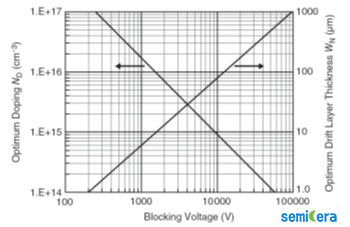

ਅੰਜੀਰ. 1. ਡੋਪਿੰਗ ਇਕਾਗਰਤਾ ਅਤੇ ਯੂਨੀਪੋਲਰ ਡਿਵਾਈਸ ਦੀ ਐਪੀਟੈਕਸੀਅਲ ਪਰਤ ਦੀ ਮੋਟਾਈ ਅਤੇ ਬਲਾਕਿੰਗ ਵੋਲਟੇਜ ਵਿਚਕਾਰ ਸਬੰਧ

SIC epitaxial ਪਰਤ ਦੀ ਤਿਆਰੀ ਦੇ ਤਰੀਕਿਆਂ ਵਿੱਚ ਮੁੱਖ ਤੌਰ 'ਤੇ ਵਾਸ਼ਪੀਕਰਨ ਵਿਕਾਸ ਵਿਧੀ, ਤਰਲ ਪੜਾਅ ਐਪੀਟੈਕਸੀਅਲ ਵਾਧਾ (LPE), ਅਣੂ ਬੀਮ ਐਪੀਟੈਕਸੀਅਲ ਵਾਧਾ (MBE) ਅਤੇ ਰਸਾਇਣਕ ਭਾਫ਼ ਜਮ੍ਹਾਂ (CVD) ਸ਼ਾਮਲ ਹਨ। ਵਰਤਮਾਨ ਵਿੱਚ, ਕਾਰਖਾਨਿਆਂ ਵਿੱਚ ਵੱਡੇ ਪੈਮਾਨੇ ਦੇ ਉਤਪਾਦਨ ਲਈ ਵਰਤਿਆ ਜਾਣ ਵਾਲਾ ਮੁੱਖ ਤਰੀਕਾ ਰਸਾਇਣਕ ਭਾਫ਼ ਜਮ੍ਹਾ (ਸੀਵੀਡੀ) ਹੈ।

| ਤਿਆਰੀ ਵਿਧੀ | ਪ੍ਰਕਿਰਿਆ ਦੇ ਫਾਇਦੇ | ਪ੍ਰਕਿਰਿਆ ਦੇ ਨੁਕਸਾਨ |

|

ਤਰਲ ਪੜਾਅ ਐਪੀਟੈਕਸੀਅਲ ਵਾਧਾ

(LPE)

|

ਸਾਧਾਰਨ ਸਾਜ਼ੋ-ਸਾਮਾਨ ਦੀਆਂ ਲੋੜਾਂ ਅਤੇ ਘੱਟ ਲਾਗਤ ਵਾਲੇ ਵਿਕਾਸ ਦੇ ਢੰਗ। |

ਐਪੀਟੈਕਸੀਅਲ ਪਰਤ ਦੀ ਸਤਹ ਰੂਪ ਵਿਗਿਆਨ ਨੂੰ ਨਿਯੰਤਰਿਤ ਕਰਨਾ ਮੁਸ਼ਕਲ ਹੈ. ਸਾਜ਼-ਸਾਮਾਨ ਇੱਕੋ ਸਮੇਂ ਕਈ ਵੇਫਰਾਂ ਦਾ ਉਪਕਰਨ ਨਹੀਂ ਕਰ ਸਕਦਾ, ਵੱਡੇ ਉਤਪਾਦਨ ਨੂੰ ਸੀਮਤ ਕਰਦਾ ਹੈ। |

|

ਮੌਲੀਕਿਊਲਰ ਬੀਮ ਐਪੀਟੈਕਸੀਅਲ ਗਰੋਥ (MBE)

|

ਵੱਖ-ਵੱਖ SiC ਕ੍ਰਿਸਟਲ ਐਪੀਟੈਕਸੀਅਲ ਪਰਤਾਂ ਨੂੰ ਘੱਟ ਵਿਕਾਸ ਤਾਪਮਾਨ 'ਤੇ ਉਗਾਇਆ ਜਾ ਸਕਦਾ ਹੈ |

ਉਪਕਰਣ ਵੈਕਿਊਮ ਲੋੜਾਂ ਉੱਚੀਆਂ ਅਤੇ ਮਹਿੰਗੀਆਂ ਹਨ। epitaxial ਪਰਤ ਦੀ ਹੌਲੀ ਵਿਕਾਸ ਦਰ |

|

ਰਸਾਇਣਕ ਭਾਫ਼ ਜਮ੍ਹਾ (CVD) |

ਫੈਕਟਰੀਆਂ ਵਿੱਚ ਵੱਡੇ ਪੱਧਰ 'ਤੇ ਉਤਪਾਦਨ ਦਾ ਸਭ ਤੋਂ ਮਹੱਤਵਪੂਰਨ ਤਰੀਕਾ। ਮੋਟੀਆਂ ਐਪੀਟੈਕਸੀਅਲ ਪਰਤਾਂ ਵਧਣ ਵੇਲੇ ਵਿਕਾਸ ਦਰ ਨੂੰ ਠੀਕ ਤਰ੍ਹਾਂ ਕੰਟਰੋਲ ਕੀਤਾ ਜਾ ਸਕਦਾ ਹੈ। |

SiC ਐਪੀਟੈਕਸੀਲ ਲੇਅਰਾਂ ਵਿੱਚ ਅਜੇ ਵੀ ਕਈ ਨੁਕਸ ਹਨ ਜੋ ਡਿਵਾਈਸ ਵਿਸ਼ੇਸ਼ਤਾਵਾਂ ਨੂੰ ਪ੍ਰਭਾਵਤ ਕਰਦੇ ਹਨ, ਇਸਲਈ SiC ਲਈ ਐਪੀਟੈਕਸੀਲ ਵਿਕਾਸ ਪ੍ਰਕਿਰਿਆ ਨੂੰ ਲਗਾਤਾਰ ਅਨੁਕੂਲ ਬਣਾਉਣ ਦੀ ਲੋੜ ਹੈ।ਟੀ.ਏ.ਸੀਲੋੜ ਹੈ, ਸੈਮੀਸੇਰਾ ਦੇਖੋTaC ਉਤਪਾਦ) |

|

ਵਾਸ਼ਪੀਕਰਨ ਵਿਕਾਸ ਵਿਧੀ

|

SiC ਕ੍ਰਿਸਟਲ ਪੁਲਿੰਗ ਦੇ ਸਮਾਨ ਉਪਕਰਣਾਂ ਦੀ ਵਰਤੋਂ ਕਰਨਾ, ਪ੍ਰਕਿਰਿਆ ਕ੍ਰਿਸਟਲ ਖਿੱਚਣ ਤੋਂ ਥੋੜ੍ਹੀ ਵੱਖਰੀ ਹੈ। ਪਰਿਪੱਕ ਉਪਕਰਣ, ਘੱਟ ਕੀਮਤ |

SiC ਦਾ ਅਸਮਾਨ ਵਾਸ਼ਪੀਕਰਨ ਉੱਚ ਗੁਣਵੱਤਾ ਵਾਲੇ ਐਪੀਟੈਕਸੀਅਲ ਲੇਅਰਾਂ ਨੂੰ ਵਧਣ ਲਈ ਇਸਦੇ ਭਾਫ਼ ਦੀ ਵਰਤੋਂ ਕਰਨਾ ਮੁਸ਼ਕਲ ਬਣਾਉਂਦਾ ਹੈ |

ਅੰਜੀਰ. 2. epitaxial ਪਰਤ ਦੇ ਮੁੱਖ ਤਿਆਰੀ ਦੇ ਢੰਗ ਦੀ ਤੁਲਨਾ

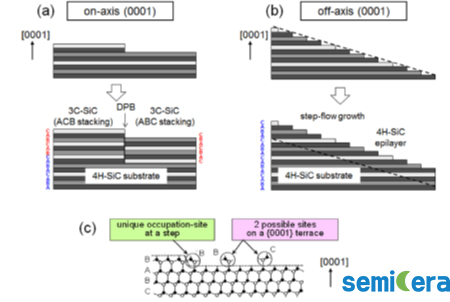

ਇੱਕ ਨਿਸ਼ਚਿਤ ਝੁਕਣ ਵਾਲੇ ਕੋਣ ਵਾਲੇ ਔਫ-ਐਕਸਿਸ {0001} ਸਬਸਟਰੇਟ ਉੱਤੇ, ਜਿਵੇਂ ਕਿ ਚਿੱਤਰ 2(b) ਵਿੱਚ ਦਿਖਾਇਆ ਗਿਆ ਹੈ, ਸਟੈਪ ਸਤ੍ਹਾ ਦੀ ਘਣਤਾ ਵੱਡੀ ਹੈ, ਅਤੇ ਸਟੈਪ ਸਤ੍ਹਾ ਦਾ ਆਕਾਰ ਛੋਟਾ ਹੈ, ਅਤੇ ਕ੍ਰਿਸਟਲ ਨਿਊਕਲੀਏਸ਼ਨ ਆਸਾਨ ਨਹੀਂ ਹੈ। ਕਦਮ ਦੀ ਸਤ੍ਹਾ 'ਤੇ ਵਾਪਰਦਾ ਹੈ, ਪਰ ਅਕਸਰ ਕਦਮ ਦੇ ਵਿਲੀਨ ਬਿੰਦੂ 'ਤੇ ਹੁੰਦਾ ਹੈ। ਇਸ ਕੇਸ ਵਿੱਚ, ਸਿਰਫ ਇੱਕ ਨਿਊਕਲੀਟਿੰਗ ਕੁੰਜੀ ਹੈ. ਇਸ ਲਈ, ਐਪੀਟੈਕਸੀਅਲ ਪਰਤ ਸਬਸਟਰੇਟ ਦੇ ਸਟੈਕਿੰਗ ਕ੍ਰਮ ਨੂੰ ਪੂਰੀ ਤਰ੍ਹਾਂ ਦੁਹਰਾਉਂਦੀ ਹੈ, ਇਸ ਤਰ੍ਹਾਂ ਬਹੁ-ਕਿਸਮ ਦੀ ਸਹਿ-ਹੋਂਦ ਦੀ ਸਮੱਸਿਆ ਨੂੰ ਖਤਮ ਕਰ ਸਕਦੀ ਹੈ।

ਅੰਜੀਰ. 3. 4H-SiC ਸਟੈਪ ਕੰਟਰੋਲ ਐਪੀਟੈਕਸੀ ਵਿਧੀ ਦਾ ਭੌਤਿਕ ਪ੍ਰਕਿਰਿਆ ਚਿੱਤਰ

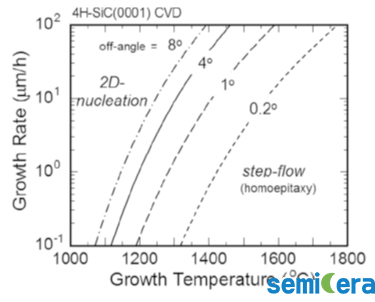

ਅੰਜੀਰ. 4. 4H-SiC ਕਦਮ-ਨਿਯੰਤਰਿਤ ਐਪੀਟੈਕਸੀ ਵਿਧੀ ਦੁਆਰਾ ਸੀਵੀਡੀ ਵਿਕਾਸ ਲਈ ਗੰਭੀਰ ਸਥਿਤੀਆਂ

ਅੰਜੀਰ. 5. 4H-SiC ਐਪੀਟੈਕਸੀ ਵਿੱਚ ਵੱਖ-ਵੱਖ ਸਿਲੀਕਾਨ ਸਰੋਤਾਂ ਦੇ ਅਧੀਨ ਵਿਕਾਸ ਦਰਾਂ ਦੀ ਤੁਲਨਾ

ਵਰਤਮਾਨ ਵਿੱਚ, ਸਿਲੀਕਾਨ ਕਾਰਬਾਈਡ ਐਪੀਟੈਕਸੀ ਤਕਨਾਲੋਜੀ ਘੱਟ ਅਤੇ ਮੱਧਮ ਵੋਲਟੇਜ ਐਪਲੀਕੇਸ਼ਨਾਂ (ਜਿਵੇਂ ਕਿ 1200 ਵੋਲਟ ਡਿਵਾਈਸਾਂ) ਵਿੱਚ ਮੁਕਾਬਲਤਨ ਪਰਿਪੱਕ ਹੈ। ਮੋਟਾਈ ਇਕਸਾਰਤਾ, ਡੋਪਿੰਗ ਇਕਾਗਰਤਾ ਇਕਸਾਰਤਾ ਅਤੇ epitaxial ਪਰਤ ਦੀ ਨੁਕਸ ਵੰਡ ਇੱਕ ਮੁਕਾਬਲਤਨ ਚੰਗੇ ਪੱਧਰ ਤੱਕ ਪਹੁੰਚ ਸਕਦੀ ਹੈ, ਜੋ ਕਿ ਮੂਲ ਰੂਪ ਵਿੱਚ ਮੱਧ ਅਤੇ ਘੱਟ ਵੋਲਟੇਜ SBD (Schottky diode), MOS (ਮੈਟਲ ਆਕਸਾਈਡ ਸੈਮੀਕੰਡਕਟਰ ਫੀਲਡ ਇਫੈਕਟ ਟ੍ਰਾਂਜ਼ਿਸਟਰ), ਜੇ.ਬੀ.ਐਸ. ਜੰਕਸ਼ਨ ਡਾਇਡ) ਅਤੇ ਹੋਰ ਯੰਤਰ।

ਹਾਲਾਂਕਿ, ਉੱਚ ਦਬਾਅ ਦੇ ਖੇਤਰ ਵਿੱਚ, ਐਪੀਟੈਕਸੀਅਲ ਵੇਫਰਾਂ ਨੂੰ ਅਜੇ ਵੀ ਬਹੁਤ ਸਾਰੀਆਂ ਚੁਣੌਤੀਆਂ ਨੂੰ ਦੂਰ ਕਰਨ ਦੀ ਲੋੜ ਹੈ। ਉਦਾਹਰਨ ਲਈ, ਉਹਨਾਂ ਡਿਵਾਈਸਾਂ ਲਈ ਜਿਹਨਾਂ ਨੂੰ 10,000 ਵੋਲਟ ਦਾ ਸਾਮ੍ਹਣਾ ਕਰਨ ਦੀ ਲੋੜ ਹੁੰਦੀ ਹੈ, ਐਪੀਟੈਕਸੀਅਲ ਪਰਤ ਦੀ ਮੋਟਾਈ ਲਗਭਗ 100μm ਹੋਣੀ ਚਾਹੀਦੀ ਹੈ। ਘੱਟ-ਵੋਲਟੇਜ ਯੰਤਰਾਂ ਦੇ ਮੁਕਾਬਲੇ, ਐਪੀਟੈਕਸੀਅਲ ਪਰਤ ਦੀ ਮੋਟਾਈ ਅਤੇ ਡੋਪਿੰਗ ਗਾੜ੍ਹਾਪਣ ਦੀ ਇਕਸਾਰਤਾ ਬਹੁਤ ਵੱਖਰੀ ਹੈ, ਖਾਸ ਕਰਕੇ ਡੋਪਿੰਗ ਗਾੜ੍ਹਾਪਣ ਦੀ ਇਕਸਾਰਤਾ। ਇਸਦੇ ਨਾਲ ਹੀ, ਐਪੀਟੈਕਸੀਅਲ ਪਰਤ ਵਿੱਚ ਤਿਕੋਣ ਨੁਕਸ ਵੀ ਡਿਵਾਈਸ ਦੀ ਸਮੁੱਚੀ ਕਾਰਗੁਜ਼ਾਰੀ ਨੂੰ ਨਸ਼ਟ ਕਰ ਦੇਵੇਗਾ। ਉੱਚ-ਵੋਲਟੇਜ ਐਪਲੀਕੇਸ਼ਨਾਂ ਵਿੱਚ, ਡਿਵਾਈਸ ਕਿਸਮਾਂ ਬਾਈਪੋਲਰ ਡਿਵਾਈਸਾਂ ਦੀ ਵਰਤੋਂ ਕਰਦੀਆਂ ਹਨ, ਜਿਸ ਲਈ ਐਪੀਟੈਕਸੀਅਲ ਲੇਅਰ ਵਿੱਚ ਉੱਚ ਘੱਟ ਗਿਣਤੀ ਦੀ ਲੋੜ ਹੁੰਦੀ ਹੈ, ਇਸਲਈ ਪ੍ਰਕਿਰਿਆ ਨੂੰ ਘੱਟ ਗਿਣਤੀ ਦੇ ਜੀਵਨ ਕਾਲ ਵਿੱਚ ਸੁਧਾਰ ਕਰਨ ਲਈ ਅਨੁਕੂਲਿਤ ਕਰਨ ਦੀ ਲੋੜ ਹੁੰਦੀ ਹੈ।

ਵਰਤਮਾਨ ਵਿੱਚ, ਘਰੇਲੂ ਐਪੀਟੈਕਸੀ ਮੁੱਖ ਤੌਰ 'ਤੇ 4 ਇੰਚ ਅਤੇ 6 ਇੰਚ ਹੈ, ਅਤੇ ਵੱਡੇ ਆਕਾਰ ਦੇ ਸਿਲੀਕਾਨ ਕਾਰਬਾਈਡ ਐਪੀਟੈਕਸੀ ਦਾ ਅਨੁਪਾਤ ਸਾਲ ਦਰ ਸਾਲ ਵਧ ਰਿਹਾ ਹੈ। ਸਿਲੀਕਾਨ ਕਾਰਬਾਈਡ ਐਪੀਟੈਕਸੀਅਲ ਸ਼ੀਟ ਦਾ ਆਕਾਰ ਮੁੱਖ ਤੌਰ 'ਤੇ ਸਿਲੀਕਾਨ ਕਾਰਬਾਈਡ ਸਬਸਟਰੇਟ ਦੇ ਆਕਾਰ ਦੁਆਰਾ ਸੀਮਿਤ ਹੁੰਦਾ ਹੈ। ਵਰਤਮਾਨ ਵਿੱਚ, 6-ਇੰਚ ਸਿਲੀਕਾਨ ਕਾਰਬਾਈਡ ਸਬਸਟਰੇਟ ਦਾ ਵਪਾਰੀਕਰਨ ਕੀਤਾ ਗਿਆ ਹੈ, ਇਸਲਈ ਸਿਲੀਕਾਨ ਕਾਰਬਾਈਡ ਐਪੀਟੈਕਸੀਅਲ ਹੌਲੀ-ਹੌਲੀ 4 ਇੰਚ ਤੋਂ 6 ਇੰਚ ਤੱਕ ਤਬਦੀਲ ਹੋ ਰਿਹਾ ਹੈ। ਸਿਲੀਕਾਨ ਕਾਰਬਾਈਡ ਸਬਸਟਰੇਟ ਤਿਆਰ ਕਰਨ ਦੀ ਤਕਨਾਲੋਜੀ ਅਤੇ ਸਮਰੱਥਾ ਦੇ ਵਿਸਥਾਰ ਦੇ ਨਿਰੰਤਰ ਸੁਧਾਰ ਦੇ ਨਾਲ, ਸਿਲੀਕਾਨ ਕਾਰਬਾਈਡ ਸਬਸਟਰੇਟ ਦੀ ਕੀਮਤ ਹੌਲੀ ਹੌਲੀ ਘੱਟ ਰਹੀ ਹੈ। ਐਪੀਟੈਕਸੀਅਲ ਸ਼ੀਟ ਦੀ ਕੀਮਤ ਦੀ ਰਚਨਾ ਵਿੱਚ, ਘਟਾਓਣਾ ਲਾਗਤ ਦੇ 50% ਤੋਂ ਵੱਧ ਲਈ ਖਾਤਾ ਹੈ, ਇਸਲਈ ਸਬਸਟਰੇਟ ਦੀ ਕੀਮਤ ਵਿੱਚ ਗਿਰਾਵਟ ਦੇ ਨਾਲ, ਸਿਲੀਕਾਨ ਕਾਰਬਾਈਡ ਐਪੀਟੈਕਸੀਅਲ ਸ਼ੀਟ ਦੀ ਕੀਮਤ ਵਿੱਚ ਵੀ ਕਮੀ ਆਉਣ ਦੀ ਉਮੀਦ ਹੈ।

ਪੋਸਟ ਟਾਈਮ: ਜੂਨ-03-2024